自己同期型FPGA

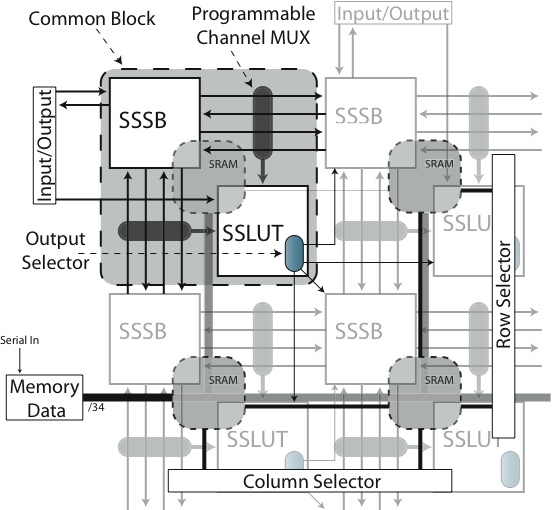

我々はデュアルパイプラインと呼ばれるアーキテクチャを用いた自己同期型FPGAを設計し,試作しています.65nmプロセスを用いて試作した 自己同期型LUTはプログラム用8ビットSRAMを備えた3入力構造です.自己同期スイッチボックスはパストランジスタとバッファーから成ります.自己同期LUTと自己同期スイッチボックスの占有面積は2.2λ2で,自己同期FPGAは34x30のブロックからなる.測定結果は32段のANDゲートで647MHz,3ビットリプルキャリー加算器で430MHzです.シミュレーション結果では1.2V,647MHzで0.642pJ/block/cycleを達成しました.