メビウス型自己同期回路

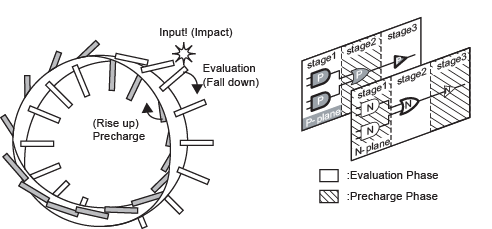

CMOS回路の微細化に伴うプロセスばらつきの増加により,同期回路設計には厳しいタイミング制約が要求され,PVTばらつきの最悪の結果として,たった一つのクリティカルパスをその他のパスが待ち続けるという状況が起こりうる.一方,自己同期回路では,パスの遅延が平均化されるような動作のため,プロセスばらつきの有無に拘らず高速動作が可能である.しかし,これまでの自己同期回路はダイナミック回路を用いているため,プリチャージ時間を必要とする.そのため,短いパイプラインやウェーブパイプラインを実装することで高速化を実現するのは非常に困難であった.ところが,”メビウス構造”を自己同期DCVSLに応用することで,プリチャージ時間は無駄にならず,レジスタを用いないでゲートレベルでのパイプラインを実現することが出来る.さらに,ハードエラーだけでなくソフトエラーまで検出することができ,エラーの起こるゲートの検出まで可能となる.