スタンダードセルレイアウトの歩留り最適化

VLSI製造プロセスの微細化に伴い、LSIの製造歩留りの低下は無視できない問題となっております。特にセルベース設計では、そのもっとも基本的な構成要素であるスタンダードセルの歩留りを向上させることで全体の歩留りの向上が望めます。本研究では、スタンダードセルレイアウトの歩留まり向上のために、与えられるタイミング制約下でレイアウト形状を変更することにより歩留りを向上させる手法について提案します。最適化アルゴリズムには線形計画法(LP; Linear Programming)を応用して用いております。

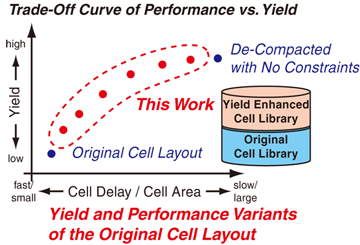

本手法により、セル遅延と歩留りとのトレードオフカーブを得ることができ、設計毎に最適なセルを選択的に生成することを可能とします。また本手法は、製造歩留り向上だけではなく、マスクパターンデータ削減やゲート長ばらつきの抑制にも応用することができ、それらの分野においても研究を進めております。