極微細CMOS技術におけるプロセスばらつきモニタ

近年のVLSIプロセス技術の進歩に伴い、1チップ上に集積できるトランジスタ数は増加の一途をたどり、回路の動作速度はますます高まっております。その一方で、VLSIの設計および検証はますます複雑となっており、同時に極微細プロセスではプロセス、電圧、温度等(PVT; Process, Voltage, and Temperature)のばらつきに対する耐性はますます低下し、さらにNegative/Positive Bias Instability(NBTI/PBTI)等のトランジスタの経年劣化によるLSIの信頼性への影響が増大しております。

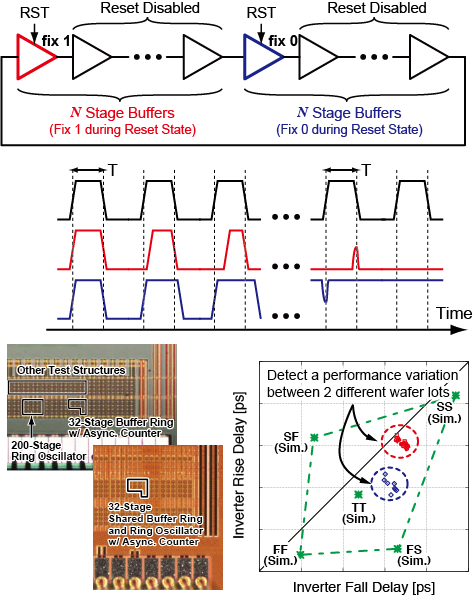

本研究では、リング型バッファチェインとパルスカウンタを用いた完全デジタル型のプロセスばらつきモニタを提案しております。提案回路ではリング型バッファチェイン内を伝搬するパルスの幅がバッファの立ち上がり・立ち下がり遅延時間に依存して変化する性質を利用し、そのパルスが消失するまでの回転数、およびパルス消失後のバッファ出力の極性をモニタすることで、立ち上がり・立ち下り時間の差を検出でき、さらに本提案回路をより一般的なのリングオシレータによる周波数モニタと合わせて使用することで、立ち上がり・立ち下がり時間の絶対値を算出することが可能となります。これによりPMOSとNMOSの性能ばらつきを独立にモニタすることが可能となります。

65nm CMOSプロセスでのシミュレーション・実測結果を用いて提案回路の性能評価を行い、プロセスばらつきモニタとしての動作を確認しております。本提案回路はPMOSとNMOSの性能を独立にモニタできることから、NBTIやPBTI等の経年劣化モニタとしても応用できる可能性があり、さらなる研究を進めております。