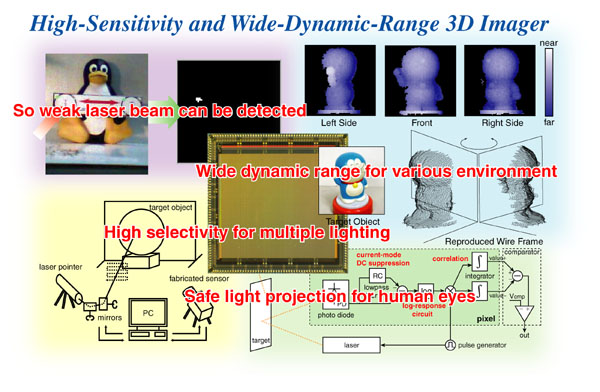

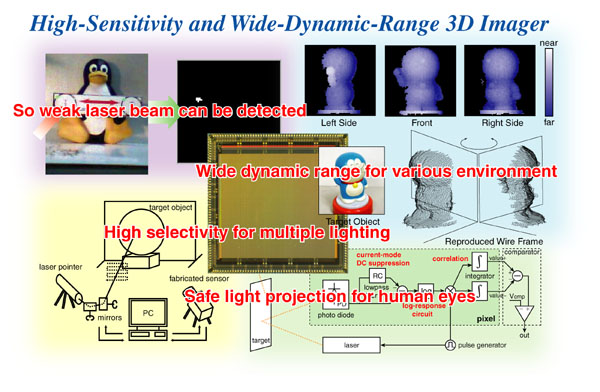

We have developed a range finder with the capability of feeble light detection

in wide range of non-uniform background illumination. It is much more applicable

to wide application field than the conventional 3-D measurement system based

on a light-section method. The latest achievement was presented at ISSCC 2003.

Y. Oike, M. Ikeda, and K. Asada,

``A 120 x 110 Position Sensor With the Capability of Sensitive and

Selective Light Detection in Wide Dynamic Range for Robust Range Finding,''

IEEE Journal of Solid-State Circuits,

Vol. 39, No. 1, pp. 246 -- 251, Jan. 2004.

[PDF]

(This achievement was partly presented in

IEEE Int. Conf. Solid-State Circuits (ISSCC), Feb. 2003.

[PDF])

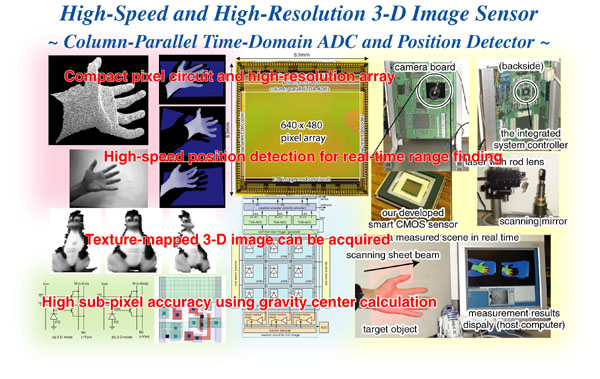

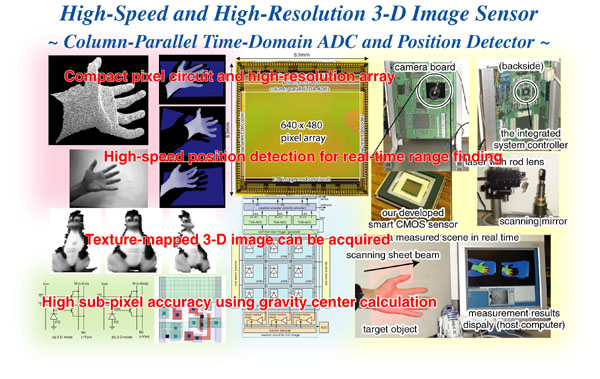

We have proposed a sensor architecture and circuit implementation

of "Smart Access", which achieves high-speed position detection of

a scanning beam for real-time 3-D measurement. For both high pixel

resolution and real time measurement, we have also proposed

a column-parallel readout scheme by an adaptive thresholding cirucit

and a time-domain approximate A/D converter. 640x480 (VGA) and

1024x768 (XGA) range finders have been developed and the measurement

system with these imagers realize "Real-Time" and "High-Accuracy"

3-D measurement.

The achievement was presented at Symp. VLSI Circuits 2003.

Y. Oike, M. Ikeda, and K. Asada,

``Design and Implementation of Real-Time 3-D Image Sensor

With 640 x 480 Pixel Resolution,''

IEEE Journal of Solid-State Circuits,

Vol. 39, No. 4, pp. 622 -- 628, Apr. 2004.

[PDF]

(This achievement was partly presented in

IEEE Symposium on VLSI Circuits (Symp. VLSI), Jun. 2003.

[PDF])

Y. Oike, M. Ikeda, and K. Asada,

``A High-Speed XGA 3-D Image Sensor and Its Applications,''

in Proc. of the 6th Biannual World Automation Congress (WAC 2004),

Jun. 2004.

[PDF]

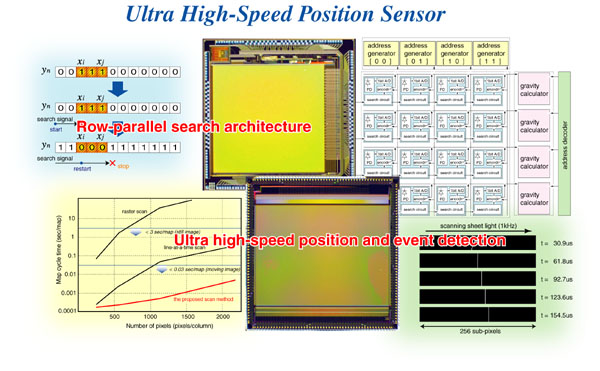

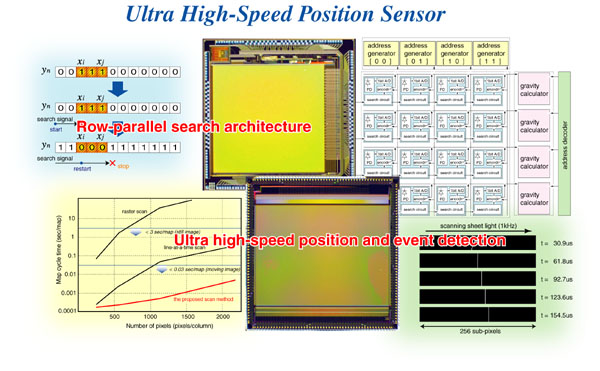

We have proposed a row-parallel position sensor

for ultra high-speed range finding.

Our sensor architecture and circuit implementation achieve

"Beyond Real-Time 3-D Imaging". It has a row-parallel position

detection circuit in each pixel and a row-parallel pre-processor

for gravity center calculation.

We have successfully tested a prototype sensor with 128x16 pixels,

which was presented at ISCAS 2003.

Furthermore a new high-speed 3-D image sensor for 1000 range maps/s

with 375 x 365 pixels has been developed.

The latest achievement was presented at ISSCC 2004.

Y. Oike, M. Ikeda, and K. Asada,

``A 375 x 365 High-Speed 3-D Range-Finding Image Sensor

Using Row-Parallel Search Architecture and Multi-Sampling Technique,''

IEEE Journal of Solid-State Circuits,

Vol. 40, No. 2, pp. 444 -- 453, Feb. 2005.

[PDF]

(This achievement was partly presented in

IEEE Int. Conf. Solid-State Circuits (ISSCC), Feb. 2004.

[PDF])

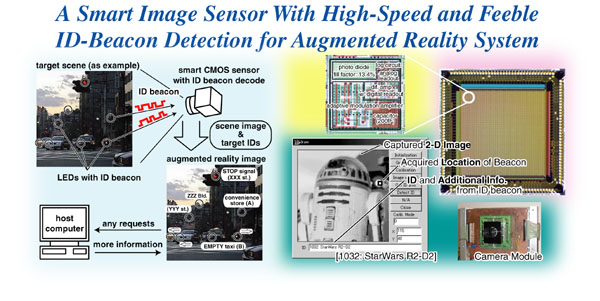

We have developed a smart image sensor with feeble ID-beacon detection

for an augmented reality (AR) system using optical active devices.

AR systems are designed to provide an enhanced view of the real

world with meaningful information from a computer.

Our image sensor achieves high-speed beacon acquisition with

ambient light suppression to realize a practical AR system.

The latest achievement was presented at ESSCIRC 2003.

Y. Oike, M. Ikeda, and K. Asada,

``A Smart Image Sensor With High-Speed Feeble ID-Beacon Detection

for Augmented Reality System,''

in Proc. of IEEE European Solid-State Circuits Conference (ESSCIRC),

pp.125 - 128, Sep. 2003.

[PDF]

We have developed a real-time 3-D imaging system using light section

method. The system has FPGA and SCSI interface for high-speed control and

data transmission. Our designed GUI software has the capability of

parameter setting, range calibration and real-time display

of acquired 3-D images.

Our achievement is the first real-time 3-D imaging system using

a light section method with VGA pixel resolution.

The latest achievement was presented at IEEE SENSORS 2003.

Y. Oike, H. Shintaku, S. Takayama, M. Ikeda, and K. Asada,

``Real-Time and High-Resolution 3-D Imaging System Using Light-Section Method

and Smart CMOS Sensor,''

in Proc. of IEEE International Conference on Sensors (IEEE SENSORS),

pp.502 - 507, Oct. 2003.

[PDF]

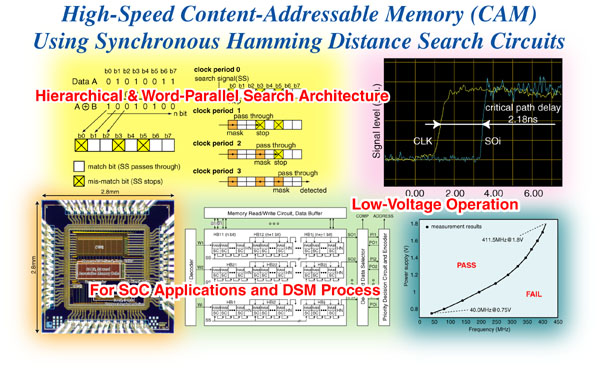

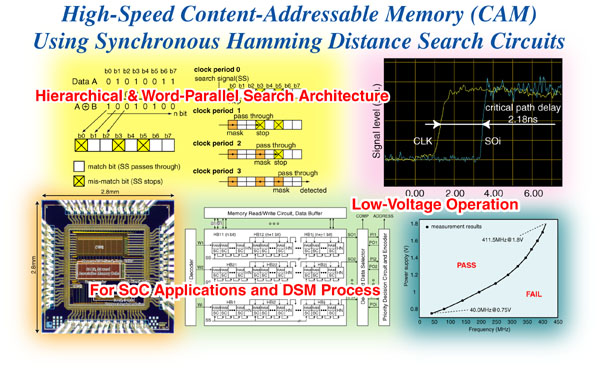

We have proposed a high-speed and low-voltage associative memory.

A hierarchical search architecture keeps high speed in large input number.

Our circuit implementation allows a low-voltage operation under 1.0V

and SoC applications,

which are difficult for the conventional analog approaches.

The search logic embedded in a memory cell realizes word-parallel Hamming

distance ordering including nearest-match detection.

The latest achievement was presented at CICC 2003.

Furthermore, we have proposed a scalable multi-chip architecture

for the high-speed digital associative memories.

Y. Oike, M. Ikeda, and K. Asada,

``A High-Speed and Low-Voltage Associative Co-Processor With

Exact Hamming/Manhattan-Distance Estimation

Using Word-Parallel and Hierarchical Search Architecture,''

IEEE Journal of Solid-State Circuits,

Vol. 39, No. 8, pp. 1383 -- 1387, Aug. 2004.

[PDF]

(This achievement was partly presented in

IEEE Custom Integrated Circuits Conf. (CICC), Sep. 2003.

[PDF])

Y. Oike, M. Ikeda, and K. Asada,

``Hierarchical Multi-Chip Architecture for High Capacity Scalability

of Fully Parallel Hamming-Distance Associative Memories,''

IEICE Trans. on Electronics,

Vol. E87-C, No. 11, pp. 1847 - 1855, Nov. 2004.

[PDF]

Y. Oike, M. Ikeda, and K. Asada,

``A Word-Parallel Digital Associative Engine

with Wide Search Range Based on Manhattan Distance,''

in Proc. of IEEE Custom Integrated Circuits Conference (CICC),

pp. 295 -- 298, Oct. 2004.

[PDF]

![]()

Go Back...

Go Back...