Self Synchronous FPGA

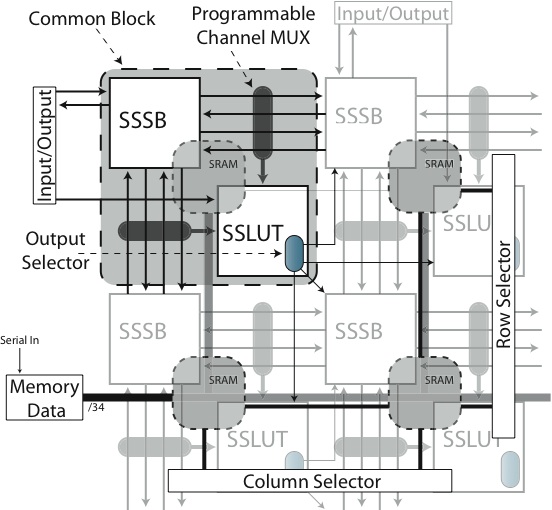

We have designed and fabricated a self synchronous field programmable gate array (SSFPGA) with dual-pipeline (DP) architecture to eliminate pre-charge time for dynamic logic. A self synchronous LUT (SSLUT) consists of a three input tree-type structure with 8 bit SRAM for programming. A self synchronous switch box (SSSB) consists of both pass transistors and buffers. One common block with one SSLUT and one SSSB occupies 2.2λ2 area and the prototype SSFPGA with 34x30 (1020) blocks is designed and fabricated using 65nm CMOS. Measured results show 647MHz operation for a chain of 32 AND gates at 1.2V and 430MHz operation for a 3 bit ripple carry adder. Simulation results show 0.642pJ/block/cycle operation at 647MHz, 1.2V.