ゲートレベルパイプライン型回路方式

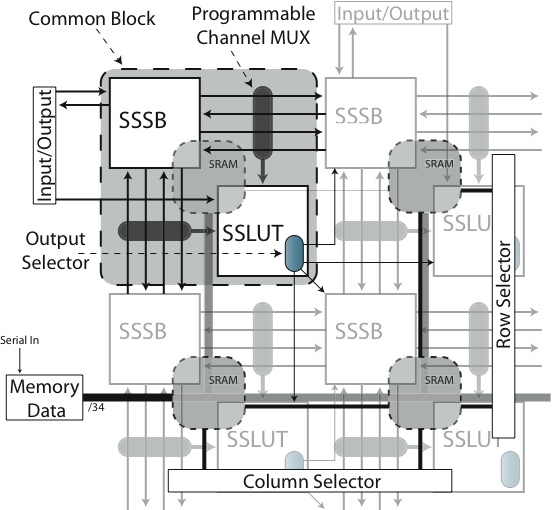

我々はデュアルパイプライン方式を活用した、ゲートごとの細粒度で回路実行の終了検出を行いそれを用いたゲートレベルで非同期制御を可能とする自己同期型回路方式の検討を行っています。その研究の一環として、自己同期型FPGAを設計し,試作しています.65nmプロセスを用いて試作した 自己同期型LUTはプログラム用8ビットSRAMを備えた3入力構造です.自己同期スイッチボックスはパストランジスタとバッファーから成ります.自己同期LUTと自己同期スイッチボックスの占有面積は2.2λ2で,自己同期FPGAは34x30のブロックからなる.測定結果は32段のANDゲートで647MHz,3ビットリプルキャリー加算器で430MHzです.シミュレーション結果では1.2V,647MHzで0.642pJ/block/cycleを達成しました.