# LSI IP デザイン・アワード応募書類表紙 (大学)

# LSI 電源用 di/dt 測定回路コア

名倉 徹<sup>†</sup>,池田 誠<sup>‡</sup>,浅田 邦博<sup>‡</sup> †東京大学 工学系研究科

‡東京大学大規模集積システム設計教育研究センター(VDEC)

技術分野:完成表彰部門(ハード設計資産)、自由課題(シグナルインテグリティ向上)

## 研究・開発の目的・狙い

半導体集積回路の製造技術の発展とともに、電源電圧の低下と消費電流の増加が同時に進行し、電源電圧に関するノイズマージンの減少を招いている。電源電圧変動は、抵抗成分と電流による IR ドロップだけでなく、インダクタンス成分と電流変化 (di/dt) によっても引き起こされるが、回路の高速化に伴い di/dt ノイズが深刻になってきている。シグナルインテグリテイ向上のために、電流変化 (di/dt) の低減とその測定方法の確立が必要とされる。これまで電源電圧変動を測定する回路は様々提案されているが、電流を測定する回路はほとんど提案されていない。今回、電源電流の di/dt を測定するオンチップ集積可能な回路コアを開発した。

### 研究・開発の概要

- 1) 利用分野: シグナルインテグリティ向上、EMI ノイズ解析。

- 2) 特徴: 相互インダクタと増幅器から構成され、オンチップ集積・リアルタイム測定が可能。

- 3) 種類: ハードウェア VC。

- 4) 性能: 9.01mA/ns の精度が得られた。

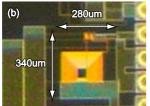

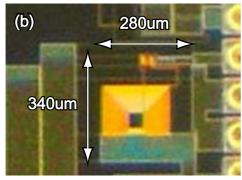

- 5) 回路規模: 340μm×280μm。

### 訴求点および効果

電源電圧変動を測定するオンチップ回路は様々提案されてきたが、電流を測定する回路に関しては、電源線に直列に抵抗を挿入してその両端の電圧を測定する方法や、磁界プローブで電流に伴って発生する磁界を測定する方法などしかなく、オンチップ集積可能な di/dt 測定法はこれまでに存在しない。今回、電源線の下にスパイラルインダクタを配置することで di/dt に比例した誘導起電力を発生させ、それを増幅器で増幅して外に取り出すことにより、リアルタイム測定が可能な di/dt 測定回路 IP を開発した。チップを試作して評価したところ、9.01mA/ns の精度が得られた。

アピールしたい指標: 革新性、実現性、適用性

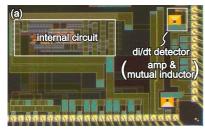

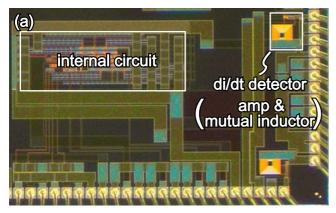

図 I: (a) チップ写真。(b)di/dt 測定回路の拡大図。

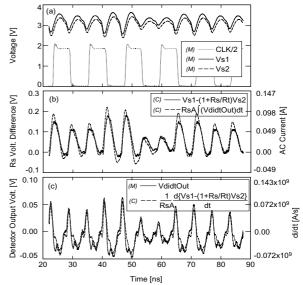

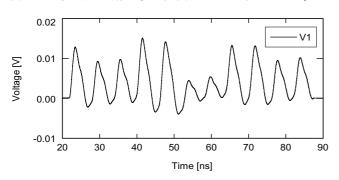

図 II: 測定波形。(a)CLK/2 と電源。(b) 電流。(c)di/dt。

## 1 はじめに

半導体集積回路の製造技術の発展とともに、電源電圧の低下と消費電流の増加が同時に進行し、電源電圧のノイズマージンが減少している。すなわち、電源ノイズがLSIにおける回路動作の信頼性を低下させている。

電源電圧変動は、抵抗成分と電流による IR ドロップだけでなく、インダクタンス成分と電流変化 (di/dt) によっても引き起こされる。そして、回路の高速化に伴ってこの di/dt ノイズの影響が深刻化している。また、近年では電磁放射ノイズ (Electro-Magnetic Interferance: EMI ノイズ) が他の LSI に悪影響を及ぼすことを懸念して、その基準が強化されており [1]、したがって、シグナルインテグリテイの向上と EMI ノイズ解析のために、電流変化 (di/dt) 測定方法の確立が必要とされている。

これまで電源電圧変動を測定する回路は様々提案されているが [2]、電流を測定する回路はほとんど提案されいない。そのうちの一つは電源線に直列抵抗を挿入してその電圧を EB(Electron Beam) プローブで測定し、その差を計算することで電流を求める方法 [3] であるが、この方法は電流や di/dt を求めるために数値計算が必要となる。電流によって発生する磁界のスペクトルを磁界プローブを用いて測定する方法もあるが、位相情報が欠けるために、元の電流および di/dt 波形を求めることができない。

今回、電源電流の di/dt を測定するオンチップ集積可能な IP を開発した [4]。また、この回路は di/dt をリアルタイムで出力することから、di/dt 制御回路などへの応用も可能である。

## 2 回路設計

### 2.1 基本原理

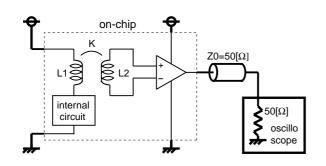

本 di/dt 測定回路の基本原理を図 1 に示す。電源電流は電源線のインダクタンス  $L_1$  を通じて内部回路に流れ込む。結合係数 K で  $L_1$  と結合されたインダクタンス  $L_2$  の

図 1: di/dt 測定の基本原理。

両端には di/dt に比例した誘電起電力が発生する。増幅器で誘導起電力を増幅し、高速測定可能な 50 オーム系の伝送線路に出力し、それをオシロスコープで観測する。

### 2.2 相互インダクタンス

インダクタンス  $L_1$  は、電源線に直列に挿入されるので小さい値を持つことが要求される。したがって、 $L_2$  の両端に十分な起電力を発生させるためには大きな結合係数 K と大きなインダクタンス  $L_2$  が必要となる。

今回は  $0.35\mu$ m、3 層メタル、2 層ポリのプロセスを用いて設計した。

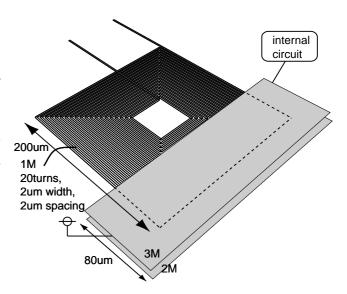

相互インダクタンスは電源線とその下に配置されたスパイラルインダクタによって構成される。図 2 に示すように、1 次側の電源線はインダクタンス  $L_1$  を抑えるために直線レイアウトとし、抵抗  $R_1$  を抑えるために ML3 と ML2 の両方を使用した。2 次側のスパイラルインダクタ

図 2: 相互インダクタの構造。

図 3: 相互インダクタの等価回路。

$L_2$  は、ML1 を用いて  $2\mu m$  幅  $\cdot 2\mu m$  スペース  $\cdot 20$  巻きで構成される。外周は  $200\mu m$  である。

3次元ソルバである FastHenry[5] を用いてこの構造の 等価回路を求めたところ、図3のようになった。

### 2.3 増幅器と出力バッファ

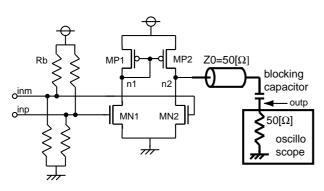

出力の di/dt 信号は高速アナログ信号であり、その増幅と出力において線形性の確保と反射を抑えることが重要となる。増幅器の回路図を図 4 に示す。電流源のないカレントミラー型の増幅器を用いた。抵抗  $R_b$  によって入力電圧を half-Vdd に DC バイアスし、増幅率と線形性を確保している。この抵抗値は十分大きく、測定周波数帯域の AC 信号に対してはオープンとして考えられる。

フィードバック方式の増幅器は、高周波応答ができなくなることと、終端抵抗である 50Ω が小さすぎて線形性と増幅率が保てなくなることが原因で、採用しなかった。

出力ピンは  $50\Omega$  系の伝送線路に直接接続される。オシロスコープの入力端子にはブロッキングキャパシタが挿入されており、 $50\Omega$  抵抗を通じてグランド接続されることによるノード n2 のバイアス電圧変化を防いでいる。電流値は有限値であるので di/dt の平均値はゼロであり、ブロッキングキャパシタは di/dt の値には影響を与えない。

HSPICE シミュレーションによると、増幅器の増幅率は 0.76 であり、負荷容量を考えない場合の遮断周波数は 3.3GHz である。線形性に関しては、出力電圧が ±0.35V の範囲で線形とみなすことができる。

図 4: 増幅器/出力バッファと測定系。

# 2.4 ノイズ源としての内部回路

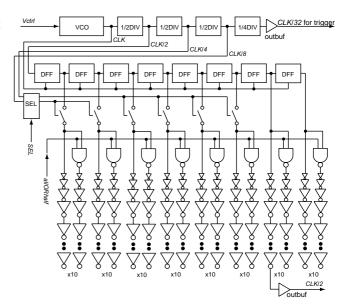

テスト用の内部回路として図5のような回路を用いた。 Vctrl 電圧を変化させることで VCO を通じて動作周波数 を変化させることができる。1/2 分周器でシフトレジスタ の入力用に CLK/2 信号を生成する。SEL 回路はリピート

図 5: 内部回路。

モードとランダムモードの切り替えに使用する。リピートモードでは SEL 回路は常に "High" を出力するため、DFF 出力の変化はインバータ列へと伝わり、毎クロックで同じ di/dt を発生する。ランダムモードでは SEL 回路は CLK/4、CLK/8 信号を出力するため、"Low" 出力の時は DFF 出力変化がインバータ列へと伝わらず、発生する di/dt の値がクロック毎に異なる。allORhalf は内部回路の活性化率を制御し、CLK/2 出力は内部回路が動作しているかのチェックに使用され、CLK/32 出力はオシロスコープのトリガとして使用する。

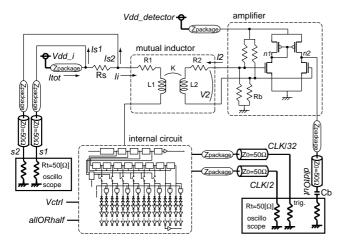

### 2.5 電源系および全体回路

di/dt 測定回路の動作比較用にオンチップ抵抗  $R_s$  を電源線に直列に挿入した。抵抗の両端は出力ピンに接続され、それぞれの電圧値を測定してその差分から電流値を計算することができ、さらに数値微分することにより、 di/dt を計算することができる。この結果を di/dt 測定回路の出力と比較する。

図 6 に示すように、電流は  $Vdd_J$  から流れ出て、パッケージやボンディングワイヤのインピーダンス  $Z_{package}$ 、直列抵抗  $R_s$ 、インダクタ  $L_1$  を通して内部回路へと流れ込む。内部回路のスイッチングによって di/dt が発生し、結合係数 K で結合されたスパイラルインダクタ  $L_2$  の両端に誘導起電力が発生する。増幅器はその起電力を増幅して didtOut へと出力する。直列抵抗  $R_s$  の両端は s1、s2端子としてオシロスコープに接続されている。 Vctrl と allORhalf は DC 信号である。 CLK/2 と CLK/32 信号は

図 6: 全体回路と測定系。

出力バッファを通じてチップの外に出力される。ただし、出力バッファ用電源 Vdd  $_{\it io}$  は図の簡略化のために省略されている。CLK/2 は回路が正常に動作しているかの確認に使用され、CLK/32 はオシロスコープのトリガとして使用される。

# 3 モデル化

# 3.1 解析式

相互インダクタンス M は

$$M = K\sqrt{L_1 L_2} \tag{1}$$

である。増幅器の入力電流を  $I_2$  とすると、誘導起電力  $V_2$  は

$$V_2 = M\frac{dI_i}{dt} + R_2I_2 + L_2\frac{dI_2}{dt} \approx M\frac{dI_i}{dt}$$

(2)

となる。ここで、増幅器の入力インピーダンスは  $R_2$ 、 $\omega L_2$  と比べて十分大きいため ( $\omega \ll 10 {

m GHz}$ )、 $I_2$  は無視できる。

増幅器の増幅率をGとすると、di/dt測定回路の出力 $V_{didtOut}$ は

$$V_{didtOut} = GV_2 = GK\sqrt{L_1L_2}\frac{dI_i}{dt}$$

(3)

であり、これは

$$\frac{dI_i}{dt} = \frac{1}{GK\sqrt{L_1L_2}}V_{didtOut} \equiv A_{v2didt}V_{didtOut} \tag{4}$$

と変形できる。ここで、

$$A_{v2didt} \equiv \frac{1}{GK\sqrt{L_1L_2}}$$

である。式 (4) を時間積分すると

$$I_i = A_{v2didt} \int V_{didtOut} dt + C$$

となる。また、内部電流  $I_i$  と電圧 s1、s2 の関係は

$$V_{s1} - V_{s2} = R_s(I_i + I_{s2}) (7)$$

であり、これは次のように変形される

$$V_{s1} - \left(1 + \frac{R_s}{R_t}\right) V_{s2} = R_s I_i \tag{8}$$

ここで、 $I_s = V_s/R_t$  であり、 $R_t$  は終端抵抗  $50\Omega$  である。式 (6) と式 (8) より、

$$V_{s1} - \left(1 + \frac{R_s}{R_t}\right) V_{s2} = R_s A_{v2didt} \int V_{didtOut} dt + C \qquad (9)$$

である。この式を時間積分することにより、

$$V_{didtOut} = \frac{1}{R_s A_{\nu 2didt}} \frac{d\{V_{s1} - (1 + R_s/R_t)V_{s2}\}}{dt}$$

(10)

が得られる。

測定可能な di/dt の範囲と周波数は増幅器の線形範囲と周波数特性によって

$$\frac{dI_i}{dt_{range}} = A_{v2didt} V_{amp\_outRange\_lin}$$

(11)

のように決まる。

# 3.2 パラメータ値

電源線の直列抵抗  $R_s$  はシリサイド化されたゲートポリシリコンによって形成され、 $2.3\Omega$  に設計した。バイアス抵抗  $R_b$  は非シリサイド化されたゲートポリシリコンによって形成され、 $10k\Omega$  である。

### 4 測定

### 4.1 測定系

チップは  $0.35\mu$ m、2 層ポリ、3 層配線の標準 CMOS プロセスを用いて製造された。チップ面積は 3.0mm×1.8mmであり、チップ写真を図 7 に示す。di/dt 測定回路の面積は  $340\mu$ m× $280\mu$ m である。

- 図8に示すように、チップを銅板上にマウントして測定した。 $Vdd_{.i}$ 、 $Vdd_{.io}$ 、 $Vdd_{.detecor}$ 、Vctrl、allORhalf は DC 電圧であり、電圧源からボード上の "島" にリード線を通じて電圧が供給され、島とそれぞれのピンが接続される。島の電圧は数個のチップ容量で固定される。didtOut、 $CLK/2\ CLK/32$ 、s1、s2 の高速出力ピンには  $50\Omega$  系の伝送線路が直接接続され、オシロスコープでの電圧観測が

- (6) 可能となっている。

図 7: (a) チップ写真。面積は 3.0mm×1.8mm。(b) di/dt 測定回路の拡大図。面積は  $340\mu$ m× $280\mu$ m。

図 8: 銅板上へのチップマウント。

#### 4.2 測定波形

図 9 にランダムモードで動作させた時の測定波形を示す。(a) は CLK/2 と s1、s2、(b) は  $V_{s1}$  –  $(1 + R_s/R_t)V_{s2}$  と、数値積分された di/dt 測定回路出力に  $R_sA_{v2didt}$  を掛けたものであり、式 (9) に基づく。 (c) は di/dt 測定回

図 9: 測定波形および計算値。(a)*CLK*/2 と *s*1、*s*2。(b) 電流波形。(c)*di/dt* 波形。ランダムモードで動作。

路出力と、 $V_{s1}$  –  $(1+R_s/R_t)V_{s2}$  を数値微分して  $R_sA_{v2didt}$  で割ったものであり、式 (10) に基づく。また、凡例中の (M) と (C) はそれぞれ測定結果と計算結果を表している。 グラフ (b)、(c) の右 Y 軸の電流、di/dt 値は  $R_s$ = $2.04<math>\Omega$ 、 $A_{v2didt}$ = $1.43\times10^9$ H $^{-1}$  として計算している。

これらの結果より、直列抵抗  $R_s$  の両端にかかる電圧差から計算される di/dt 値と di/dt 測定回路出力とが一致していることから、di/dt 測定回路が設計通りに動作していることがわかる。

### 4.3 測定精度

直列抵抗の値 $R_s$  は、抵抗の電圧 s1 と s2 の電圧差  $\Delta V$  から計算される。より低速で動作させた場合、CLK/2 エッジの直前では内部回路は動作しておらず、そのリーク電流を無視すると直列抵抗 $R_s$  に流れる電流は s2 出力の終端抵抗 $R_t$  に流れる電流と同じであり、 $I_{s2} = V_{s2}/R_t$  である。したがって、直列抵抗の値は  $R_s = \Delta V/I_{s2} = R_t \Delta V/V_{s2} = 2.04 \Omega$ として求めた。 $R_s$  のおおよその設計値は  $2.3 \Omega$  であり、測定値である  $2.04 \Omega$  は正しいと考えられる。

図 9(b)(c) における実線と点線との誤差は、ランダムパターンの繰り返しである *CLK*/16 周期 (22ns から 72ns)

における

$$\sigma = \sqrt{\frac{1}{N-1} \sum_{i=1}^{N} (V_{solid} - V_{dashed})^2}$$

(12)

によって評価することにする。ここで、サンプリング点は約 750 点である。図 9(b) における誤差は  $\sigma$ =9.10mV であり、これは 4.46mA に相当し、図 9(c) における誤差は  $\sigma$ =6.30mV であり、9.01mA/ns に相当する。

# 4.4 入力インピーダンス

相互インダクタの 1 次側  $L_1$  と  $R_1$  は電源線に直列に挿入されるため、そのインピーダンスは内部回路の電源ノイズを引き起こす。HSPICE シミュレーションによるdi/dt 測定回路での電圧降下波形を図 10 に示す。ただし、図 3 に示す等価回路と図 9(b) の点線で示される電流値を用いた。

本測定回路を挿入したことによる電圧降下は 15mV 程度であり、実用に耐えうる程度であると考えられる。

図 10: di/dt 測定回路の電圧降下。HSPICE によるシミュレーション結果。

### 4.5 律則要因および将来性

本 di/dt 測定回路の律則要因として以下のものが挙げられる。

- 1. 増幅器の周波数応答 ( $\omega_{cut} > \omega_{didt}$ )

- 2. 2 次側コイルのインピーダンスと負荷容量 ( $|R_2+j\omega_{didt}L_2|<1/\omega_{didt}C_{load}$ )

- 3. 2 次側コイルのインピーダンスと負荷・寄生容量との共振周波数  $(\omega_{didt} < 1/\sqrt{L_2C})$  ここで、負荷容量とは増幅器の入力容量であり、寄生容量とは 2 次コイルと基板との容量、隣接コイルとの容量など

上記の 2. および 3. はプロセスが進んでも変化は小さいが、本 di/dt 測定回路の律則となっている 1. 増幅器の 遮断周波数は上昇する。したがって、プロセスの微細化にともなって測定回路の性能は向上し、ある段階で 2. もしくは 3. で律則されることになる。

## 5 まとめ

LSI 電源の di/dt 測定回路 IP を開発した。本 di/dt 測定用 IP の出力と、動作比較用に電源線に挿入した抵抗の両端の電圧差から計算される di/dt の値がよく一致することから、本 IP が設計通りに動作していることが確認できた。最後に本 IP の特性を表 1 にまとめた。

表 1: di/dt 測定回路 IP の特性

| 面積        | $280\mu m \times 340\mu m$       |

|-----------|----------------------------------|

| 必要ピン数     | 3 (di/dt 出力、増幅器用 Vdd·Gnd)        |

| 入力インピーダンス | $R$ =0.14 $\Omega$ , $L$ =0.26nH |

| 精度        | 10mA/ns                          |

| 測定可能範囲    | ±500mA/ns                        |

| 最高周波数     | $f_{cut}$ =3.3GHz                |

# 謝辞

本チップ試作は東京大学大規模集積システム設計教育研究センターを通し、ローム(株)および凸版印刷(株)の協力で行われたものである。

## 参考文献

- [1] "Agreement of Voluntary Control Council for Interference by Information Technology Equipment,"

Voluntary Control Council for Interference by Information Technology Equipment (VCCI) [Online]

http://www.vcci.or.jp/vcci.e/member/kiyaku/kiyaku.html

- [2] Makoto Takamiya, Masayuki Mizuno, Kazuyuki Nakamura, "An on-chip 100GHz-sampling rate 8-channel sampling oscilloscope with embedded sampling clock generator," *IEEE Int. Solid-State Circuit Conf. Dig. Tech. Papers*, Feb. 2002, pp.182–183.

- [3] Keith A. Jenkins, Robert L. Franch, "Measurement of VLSI Power Supply Current by Electron-Beam Probing," *IEEE J. Solid-State Circuits*, pp.948–950, June 1992.

- [4] Toru Nakura, Makoto Ikeda, Kunihiro Asada, "Power Supply di/dt Measurement using On-chip di/dt Detector Circuit," *IEEE/JSAP Symposium on VLSI Circuits*, sess.7-4, pp.106-109, June 2004.

- [5] "FastHenry USER'S GUIDE," [Online] http://rleweb.mit.edu/vlsi/codes.htm